| DIGITAL DESIGN COEN 312                    | Instructor: Drs. A. J. Al-Khalili & M. Nekil |

|--------------------------------------------|----------------------------------------------|

| Final exam. May 2000                       | Time Allowed 3:00 hrs.                       |

| No. of pages: 2                            |                                              |

| No Calculators, books or notes are allowed |                                              |

| No Calculators, books or notes are allowed |                                              |

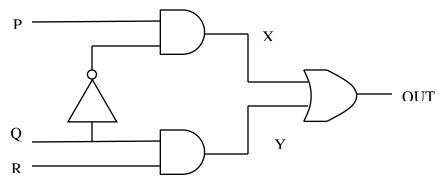

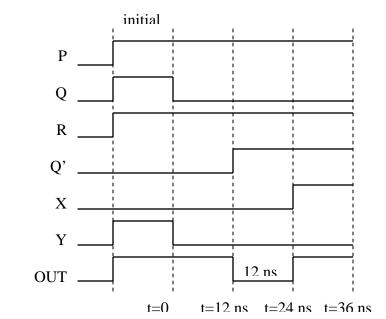

- a) Consider the circuit given in Fig. 1 below. Assume each gate, including the inverter has a 12 ns  $t_{pd}$ . The inputs are currently POR = 111. How does the OUT responds when Q makes a sudden change from HI to LO.

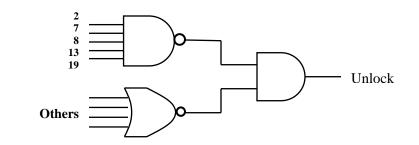

- b) A safe has 20-button keyboard. In order to unlock the safe, a teller must simultaneously press buttons 2,7,8,13, and 19. If extra buttons are pressed at the same time, the safe will not unlock. When a button is pressed, it can send a HI output to a logic circuit. Design a combinational circuit where HI output will represent the unlocked safe. Assume you have independent access to each digitized key.

- c) Prove the De Morgan Theorem.

Fig. 1 Circuit for timing Analysis of Q.1a

#### Question 2

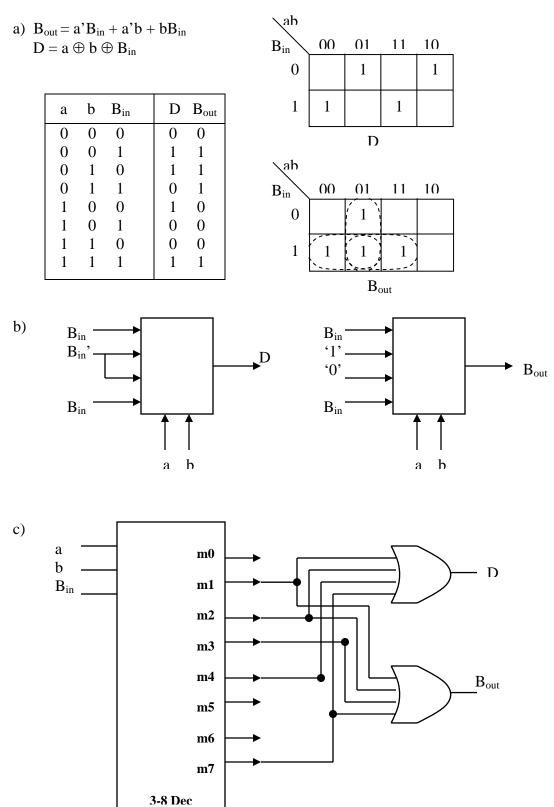

- a) Design a full subtractor

- b) Implement a) above using  $4 \rightarrow 1$  Multiplexers and minimal extra logic if required.

- c) Implement a) above using  $3 \rightarrow 8$  decoder and minimal extra logic if required

Question 3

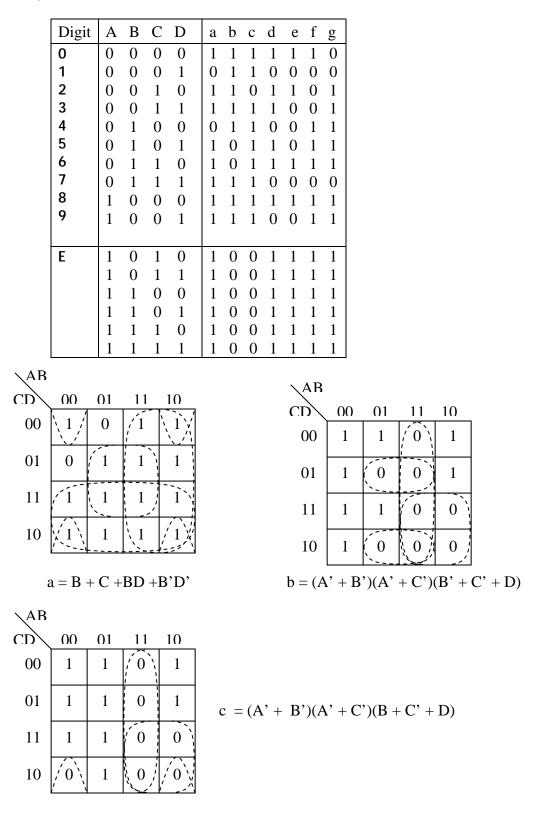

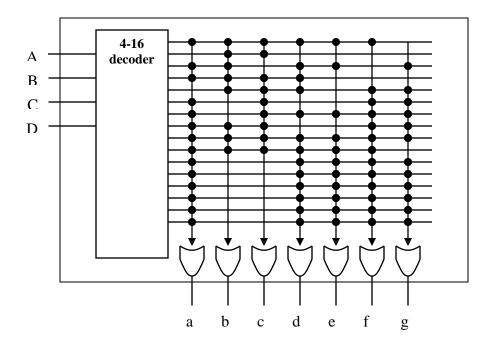

- a) What size of ROM is required to implement a BCD to 7-segment decoder.

- b) Design a BCD to 7-segment decoder. Given the content of the Rom IN A TABLE FORMAT. With each word as, abcdefg. Please refer to Fig. 2 below for the segment's destination. Assume that the illegal numbers will be displayed as E.

Fig. 2. 7-Segment Display of Q3

a) Design an adder that can add two BCD numbers.

b) Give a circuit Diagram

### Question 5

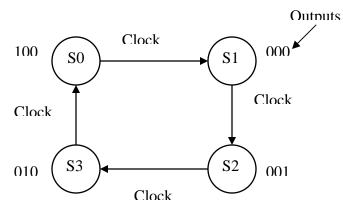

An engine needs to go through four strokes, all of equal duration.

On the 1<sup>st</sup> stroke the inlet valve opens and outlet valve is closed.

On the  $2^{nd}$  stroke the value is closed.

On the 3<sup>rd</sup> stroke a spark is delivered.

On the 4<sup>th</sup> stroke the outlet valve is opened for the exhaust to vent.

Then the first stroke comes again and the cycle repeats.

Design a controller for the system with a clock for the input and with 3 outputs:

O1 to open inlet

O2 to open outlet

O3 to ignore spark

Assume that if the control to open a valve is not asserted the valve closes (ie. Spring loaded).

Question 6

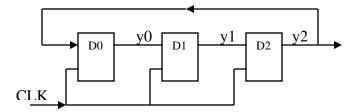

- a) Analyze the circuit given in Fig. 3 below fully (give excitation equations, transition table, state table and state diagram):

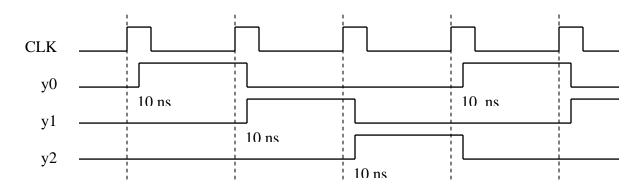

- b) Initially Do has been set to "1" (for one clock period). Draw the timing diagram for y0, y1, y2 for 5 clock cycles. Assume each Flip flop has a delay of 10 ns.

Fig. 3. Circuit to be analyzed in Q.6.

# **Solutions**

b)

c) (A.B)' = A' + B'By Truth Table

| Α | В | A.B | (A.B)' | A' | B' | A' + B' |     |

|---|---|-----|--------|----|----|---------|-----|

| 0 | 0 | 0   | 1      | 1  | 1  | 1       |     |

| 0 | 1 | 0   | 1      | 1  | 0  | 1       |     |

| 1 | 0 | 0   | 1      | 0  | 1  | 1       |     |

| 1 | 1 | 1   | 0      | 0  | 0  | 0       |     |

|   |   |     |        |    |    |         |     |

|   |   |     |        |    |    |         | Equ |

Question 3

a) 10 words of 7 bits = 70 bits with error bits

**ROM Implementation:**

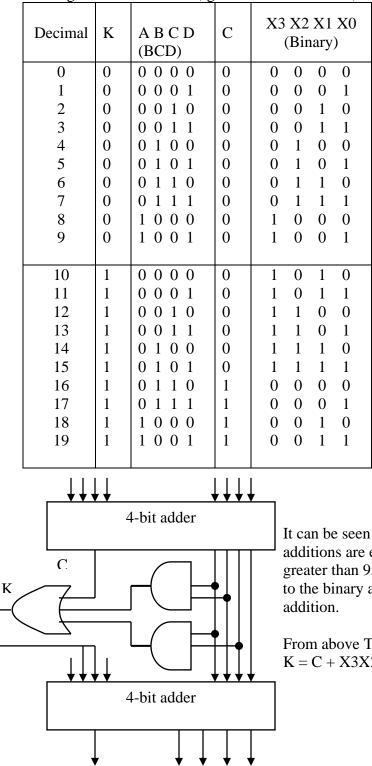

| Adding two BCD numbers,   | give a | maximum | of 19  | ie9   | +9+1=19                |

|---------------------------|--------|---------|--------|-------|------------------------|

| mulling two DCD nullious, | SIVUU  | maximum | or 17, | 1.0 ) | $  \mathbf{j}   1 = 1$ |

It can be seen that from 0-9 the two additions are equal. For numbers greater than 9, we had add a 6 (0110) to the binary addition to get the BCD addition.

From above Truth Table, we have: K = C + X3X2 + X3X1.

There are four states, are for each stroke, output are O1 O2 O3.

This is a simple counter  $S0 \rightarrow S1 \rightarrow S2 \rightarrow S3 \rightarrow S0 \rightarrow ...$

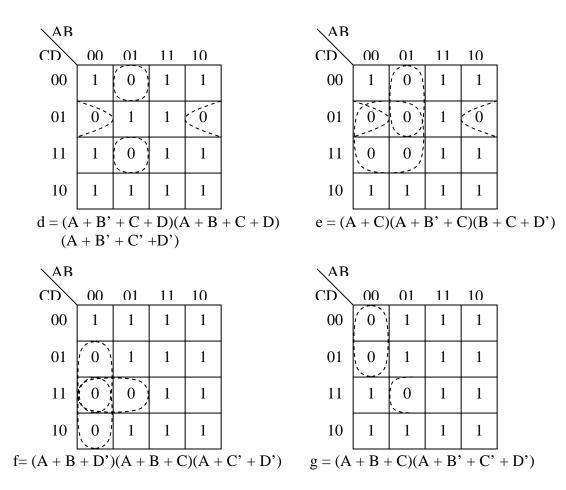

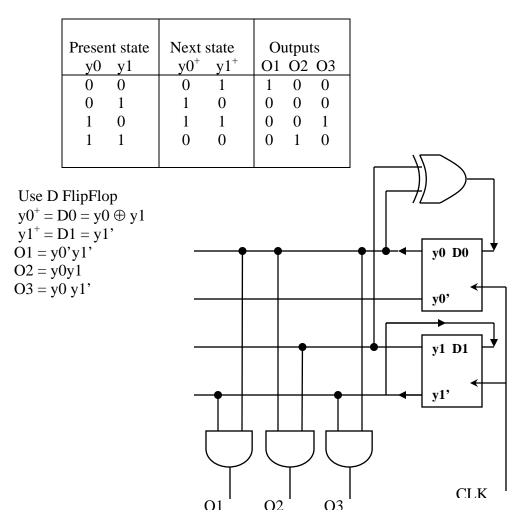

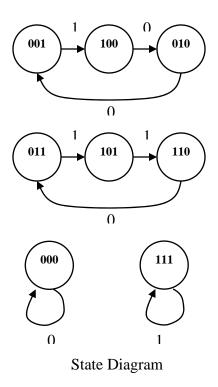

a) Excitation Equations  $y0^+ = D0 = y2$

$y0^+ = D0 = y2$   $y1^+ = D1 = y0$   $y2^+ = D2 = y1$ Output = Z = y2

Transition Table and State Table

| Present State<br>y0 y1 y2 | Next state $y0^+ y1^+ y2^+$ | Output<br>Z |

|---------------------------|-----------------------------|-------------|

| 0 0 0                     | 0 0 0                       | 0           |

| 0 0 1                     | 1 0 0                       | 1           |

| 0 1 0                     | 0 0 1                       | 0           |

| 0 1 1                     | 1 0 1                       | 1           |

| 1 0 0                     | 0 1 0                       | 0           |

| 1 0 1                     | 1 1 0                       | 1           |

| 1 1 0                     | 0 1 1                       | 0           |

| 1 1 1                     | 1 1 1                       | 1           |

## Timing Diagram